# Code-generator of parallel assembly code for digital signal processor

Bukharenko Nikita

## Problems

- The necessity of developing programs on lowlevel language (assembler)

- Getting an inefficient code after translating program from C/C++ to assembly language

- The necessity of manual parallelization of assembly code

## Approach to the solution

The scheme - is the natural representation of the digital signal processing problem

- There is no need to represent it in text form

- The scheme naturally shows the parallelism

### The purpose

# Code-generator of parallel assembly code according to the scheme of objects for microprocessor's DSP-core

### Tasks

- Targeting to different instruction sets

- Generating parallel and sequential code (singlethreaded cores only)

- Optimization of registers and memory work

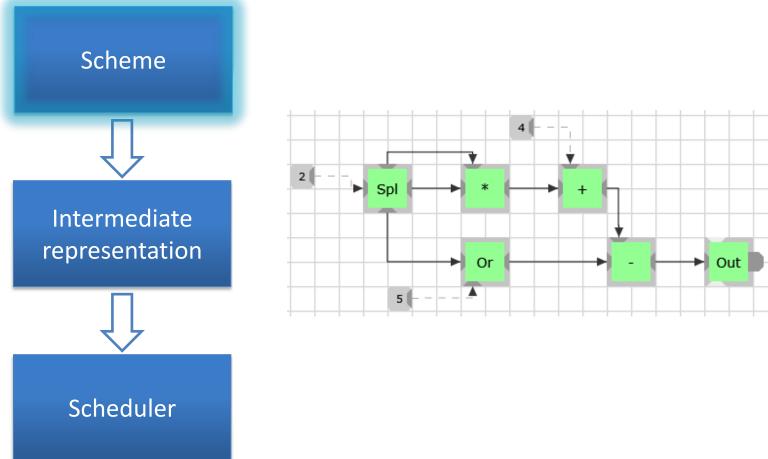

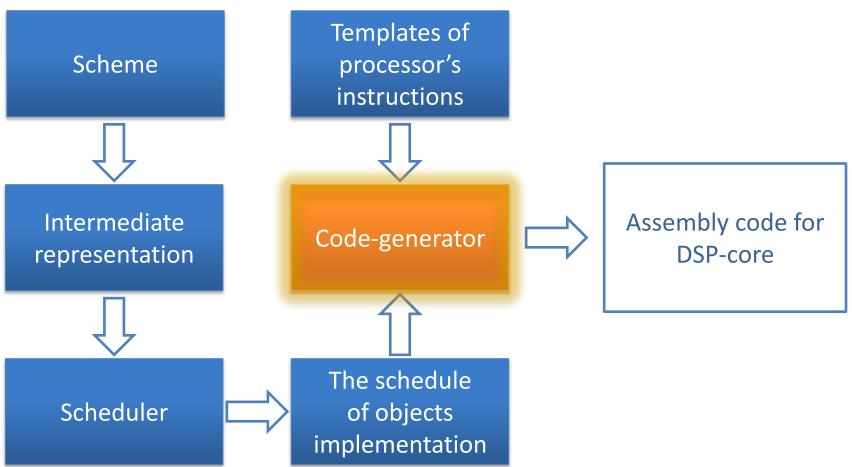

# The scheme of the code-generator's environment

# The scheme of the code-generator's environment

array

for

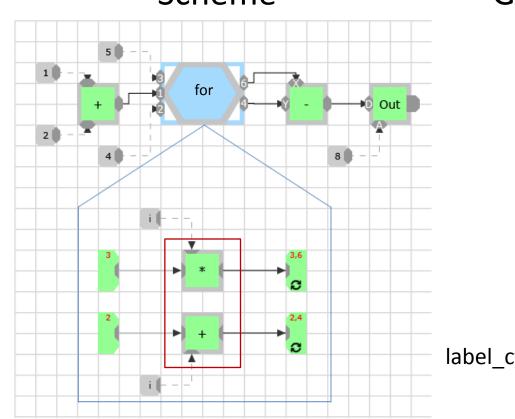

Scheme

Intermediate

representation

Scheduler

Code generator supports the scheme with such operators :

Computing operators

Data objects

(variables, data)

Cycles

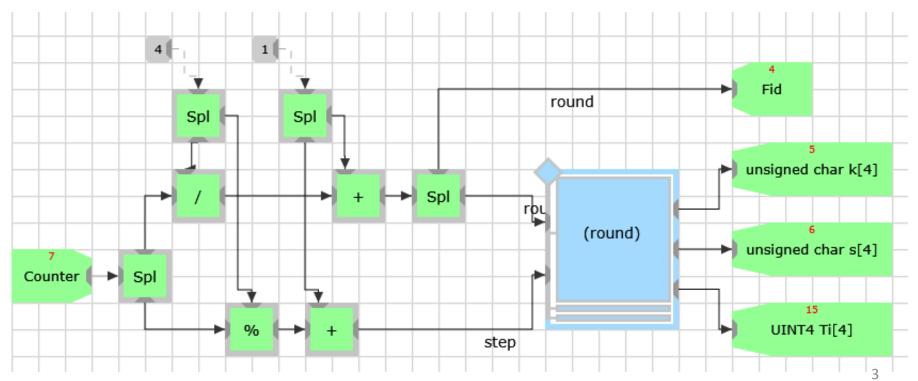

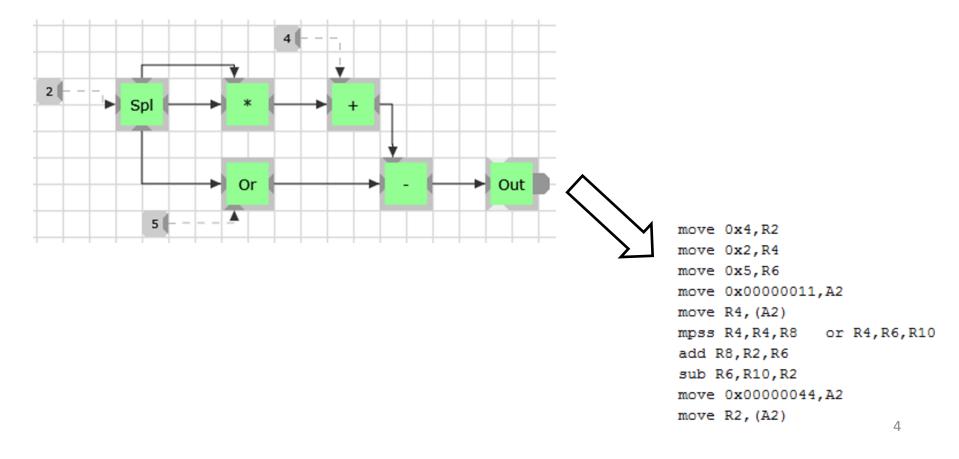

#### The scheme of the code-generator's environment 4 ٦. Spl 2 Out Or 5 (5) (2) (3) (6) **(1)** į The schedule Scheduler of objects implementation

### The scheme of the code-generator's environment Templates of

Scheme

processor's instructions

An example of **multiplication's** template for DSP-core:

An example of **subtraction's** template for DSP-core:

entity llmul [dsp2] is mpss &regin1,&regin2,&regout1 entity llmul end. entity llsub [dsp1] is sub &reginx1,&reginy1,&regout1 entity llsub end.

# The scheme of the code-generator's environment

## Optimization

The main directions in the optimization of the output code:

- Optimization of memory usage(to minimize memory access)

- Optimization of general purpose registers usage (economical usage of a limited set of registers)

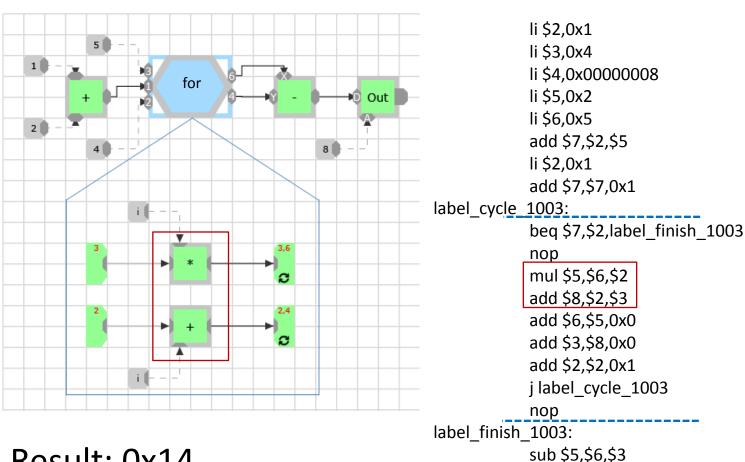

### An example of code-generator's work for DSP-core Scheme

Result: 0x14

Generated code

move 0x1,R2 move 0x4,R4 move 0x0000008,R6 move 0x2,R8 move 0x5,R10 add R2,R8,R12 move 0x1,R2 do R12, label\_cycle\_1003 mpss R10,R2,R8 add R2,R4,R14 move R8,R10 move R14,R4 label cycle 1003: inc R2,R2 sub R4,R10,R8 move R6,A0 move R8,(A0)

#### An example of code-generator's work for RISC-core Scheme Generated code

Result: 0x14

sw \$5,0(\$4)

## Resume

- Visual scheme instead of text code

- Explicit parallelism at the level of the scheme

- An efficient parallel assembly code

- Targeting to different processors and instruction sets

## Thank you for your attention!