You are here

R&D in Hardware For Embedded Systems and SoC design

SpaceWire technology for Integrated Modular Spacecraft Avionics

- The SpaceWire standard ECSS-E-50-12A was developed by international efforts, under the European Space Agency project.

- The SUAI participates in the SpaceWire Working Group standard development activities.

- SpaceWire is based on the IEEE1355-1995 and TIA/EIA-644 standards with adaptation for aerospace requirements:

- compact implementation in chips,

- reliability,

- low power consumption,

- EMC requirements, etc.

Chipset with SpaceWire for aerospace applications

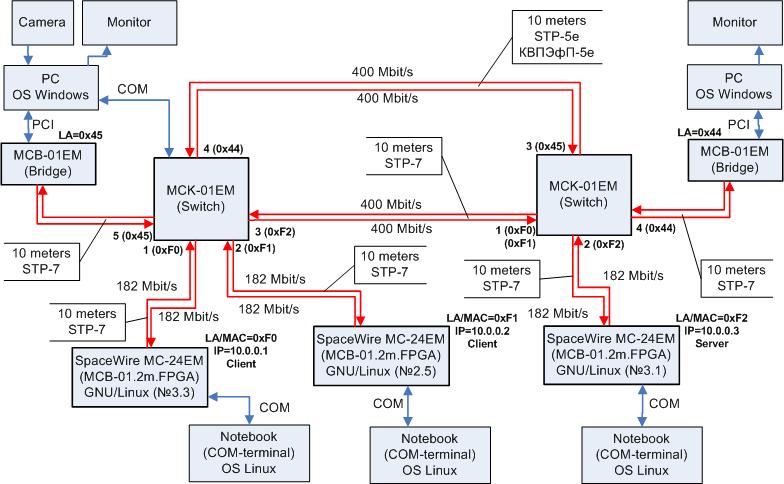

Breadboard of Complex Distributed High-Speed Communication System Based on SpaceWire Technology

Structure chart of the model

A model is an example of developing of a distributed system on the basis of communications SpaceWire (ECSS-E-50-12A). There are five computers in the system only for demonstration purpose. Video stream is send from one computer over SpaceWire network to another computer. Three notebooks show a state of OS Linux. One SpaceWire MC24EM bridge is ftp-http-server, two other SpaceWire MC24EM bridges are clients.

PCB SpaceWire MC-24EM

|

Debug package of a SpaceWire bridge (MCB-01.2m.FPGA) |

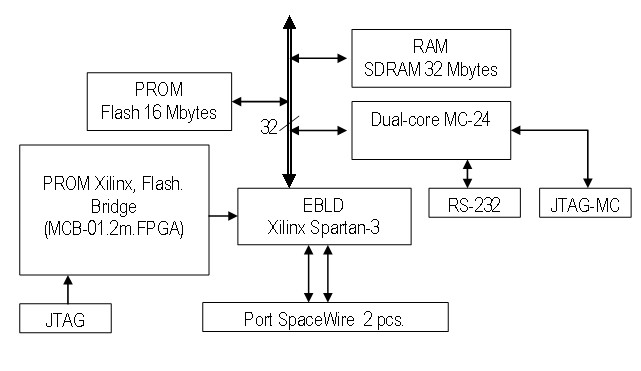

Structure chart of PCB |

PCB SpaceWire MC-24EM may be used as computing unit with incorporated 2-channel SpaceWire bridge (MCB 01.2m.FPGA). Both features of a digit unit and communicational hardware make it possible to develop different distributed computing systems and parallel systems of processing signals and data on the basis of these PCB. SpaceWire bridge (MCB-01.2m.FPGA) Being configured as SpaceWire bridge, PCB is a combination of computing unit and 2 channel bridge. The bridge makes it possible for the processor to work with 2 SpaceWire channels. This bridge maintains receive/transmit of packets, time-codes, codes of distributed interruptions, codes of distributed interrupt acknowledgement. The processor requires a driver to work with the bridge. Processor itself runs the driver code.

MCB-01.2.ASIC (1892ХД1Я) 4 channel SpaceWire bridge

|

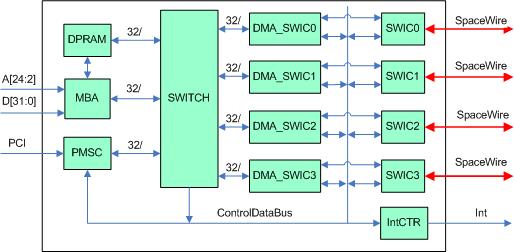

Structure of MCB-01.2.ASIC |

General features |

MCB-01.2.ASIC chip photo

VLSI MCB-01.2.ASIC is intended for construction scale communicational structures (networks SpaceWire) with high throughput on the base of protocols SpaceWire for distibuted computing and control systems, parallel systems of signal and data processing.

MCB-01.2m.FPGA 2 channel SpaceWire bridge

|

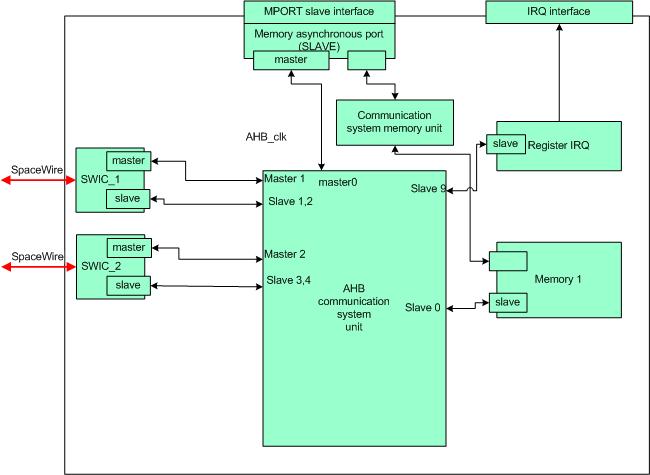

Structure of MCB-01.2m.FPGA |

General features |

VLSI MCB-01.2m.FPGA is intended for construction scale communicational structures (networks SpaceWire) with high throughput on the base of protocols SpaceWire for distributed computing and control systems, parallel systems of signal and data processing.

MCK-01.ASIC (1892ХД2Я) 16 channel SpaceWire routing switch

|

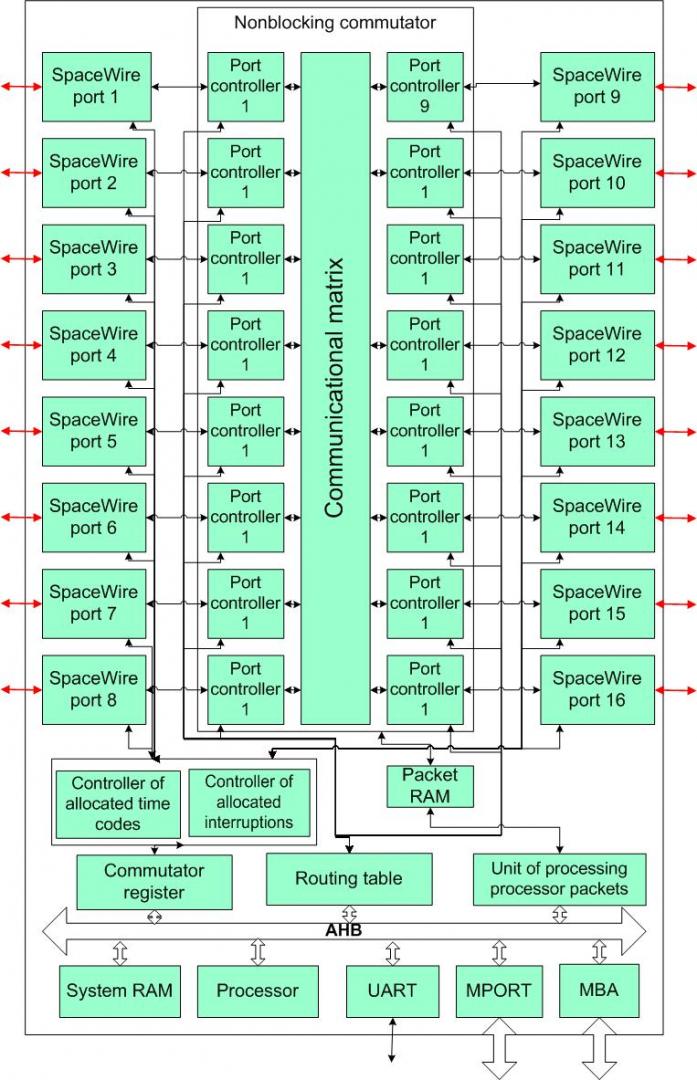

Structure of MCK-01.ASIC |

General features |

MCK-01.ASIC chip photo

VLSI MCK-01.ASIC is intended for construction scale communicational structures (networks SpaceWire) with high throughput on the base of protocols SpaceWire for distributed computing and control systems, parallel systems of signal and data processing.

|

|

|

.jpg)